# MAX32660 USER GUIDE

UG6659; Rev 0; 7/18

**Abstract:** This user guide provides application developers information on how to use the memory and peripherals of the MAX32660 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing the clocks, power and initialization of the product.

# **Table of Contents**

| 1 | Introdu            | ction                                                       | . 13 |

|---|--------------------|-------------------------------------------------------------|------|

|   | 1.1 Relat          | ed Documentation                                            | 13   |

| 2 | Overvie            | w                                                           | . 13 |

| 3 |                    | y, Register Mapping, and Access                             |      |

|   |                    | view                                                        |      |

|   |                    | dard Memory Regions                                         |      |

|   | 3.2.1              | Code Space                                                  |      |

|   | 3.2.2              | SRAM Space                                                  |      |

|   | 3.2.3              | Peripheral Space                                            |      |

|   | 3.2.4<br>3.3 Devi  | System Area (Private Peripheral Bus)<br>ce Memory Instances |      |

|   |                    | -                                                           |      |

|   | 3.3.1<br>3.3.2     | Main Program Flash Memory<br>Instruction Cache Memory       |      |

|   | 3.3.3              | System SRAM                                                 |      |

|   | 3.3.4              | AHB Bus Matrix and AHB Bus Interfaces                       | 18   |

|   | 3.3.5              | Core AHB Interface                                          |      |

|   | 3.3.6<br>3.4 Perin | AHB Master<br>heral Register Map                            |      |

|   |                    |                                                             |      |

| 4 |                    | Clocks, Reset, and Power Management                         |      |

|   |                    | Operating Voltage Range Selection                           |      |

|   | 4.1.1<br>4.1.2     | Setting the Operating Voltage Range<br>Flash Wait States    |      |

|   | =                  | em Clocks                                                   |      |

|   |                    | llator Sources and System Clock Selection                   |      |

|   | 4.3.1              | High-Frequency Internal Oscillator                          | 26   |

|   | 4.3.2              | 32.768kHz External Crystal or Clock                         | 26   |

|   | 4.3.3              | 8kHz Ultra-Low Power Nano-Ring Internal Oscillator          |      |

|   |                    | em Oscillators Reset<br>rating Modes                        |      |

|   | 4.5.1              | ACTIVE Mode                                                 |      |

|   | 4.5.2              | SLEEP Low Power Mode                                        |      |

|   | 4.5.3              | DEEPSLEEP Low Power Mode                                    |      |

|   | 4.5.4              | BACKUP Low Power Mode                                       |      |

|   | 4.5.5<br>4.6 Shut  | Wake-Up Sources<br>down State                               |      |

|   |                    | ce Resets                                                   |      |

|   | 4.7.1              | Peripheral Reset                                            | 29   |

|   | 4.7.2              | Soft Reset                                                  |      |

|   | 4.7.3              | System Reset                                                |      |

|   | 4.7.4<br>4.8 Instr | Power-On Reset<br>uction Cache Controller                   |      |

|   |                    |                                                             |      |

|   | 4.8.1<br>4.8.2     | Enabling ICCO<br>Disabling ICCO                             |      |

|   | 4.8.3              | Flushing the ICCO Cache                                     |      |

|   |                    | ) Registers                                                 |      |

|   | 4.9.1              | ICCO Register Details                                       | 31   |

|   | 4.10                                                                                                                                                                                                          | RAM Memory Management                                                                                                                                                                                                                                                                                                                 | 32                                                                                                             |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   | 4.10.1                                                                                                                                                                                                        | On-Chip Cache Management                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|   | 4.10.2                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 4.10.3<br>4.11                                                                                                                                                                                                | Global Control Registers (GCR)                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|   |                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

|   | 4.11.1<br>4.12                                                                                                                                                                                                | Global Control Register Details<br>System Initialization Registers                                                                                                                                                                                                                                                                    |                                                                                                                |

|   |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 4.12.1<br>4.13                                                                                                                                                                                                | System Initialization Register Details<br>Function Control Registers                                                                                                                                                                                                                                                                  |                                                                                                                |

|   |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 4.13.1<br>4.14                                                                                                                                                                                                | Function Control Register Details<br>Power Supply Monitoring                                                                                                                                                                                                                                                                          |                                                                                                                |

|   | 4.15                                                                                                                                                                                                          | Power Sequencer Registers                                                                                                                                                                                                                                                                                                             |                                                                                                                |

|   | 4.15.1                                                                                                                                                                                                        | Power Sequencer Register Details                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 5 |                                                                                                                                                                                                               | Controller                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|   | 5.1.1                                                                                                                                                                                                         | Features                                                                                                                                                                                                                                                                                                                              | 51                                                                                                             |

|   |                                                                                                                                                                                                               | /erview                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

|   |                                                                                                                                                                                                               | age                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

|   | 5.3.1                                                                                                                                                                                                         | Clock Configuration                                                                                                                                                                                                                                                                                                                   | 51                                                                                                             |

|   | 5.3.2                                                                                                                                                                                                         | Lock Protection                                                                                                                                                                                                                                                                                                                       | 52                                                                                                             |

|   | 5.3.3                                                                                                                                                                                                         | Flash Write Width                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

|   | 5.3.4<br>5.3.5                                                                                                                                                                                                | Flash Write                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

|   | 5.3.5<br>5.3.6                                                                                                                                                                                                | Page Erase<br>Mass Erase                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|   |                                                                                                                                                                                                               | ish Controller Registers                                                                                                                                                                                                                                                                                                              |                                                                                                                |

|   |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

| 6 | Gene                                                                                                                                                                                                          | ral-Purpose I/O and Alternate Function Pins                                                                                                                                                                                                                                                                                           | . 58                                                                                                           |

|   |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

|   | 6.1 G                                                                                                                                                                                                         | ral-Purpose I/O and Alternate Function Pins<br>neral Description<br>wer-On-Reset Configuration                                                                                                                                                                                                                                        | 58                                                                                                             |

|   | 6.1 G                                                                                                                                                                                                         | neral Description                                                                                                                                                                                                                                                                                                                     | 58<br>59                                                                                                       |

|   | 6.1 Go<br>6.2 Pc<br>6.2.1<br>6.2.2                                                                                                                                                                            | neral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration                                                                                                                                                                                                              | 58<br>59<br>60<br>60                                                                                           |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                                                                                    | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration                                                                                                                                                                                | 58<br>59<br>60<br>60<br>60                                                                                     |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                                           | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength                                                                                                                                                         | 58<br>59<br>60<br>60<br>60                                                                                     |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al                                                                                                                                                 | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration                                                                                                                       | 58<br>59<br>60<br>60<br>60<br>61                                                                               |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Co                                                                                                                                       | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration<br>infiguring GPIO (External) Interrupts                                                                              | 58<br>59<br>60<br>60<br>60<br>61<br>61                                                                         |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1                                                                                                                              | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration<br>Infiguring GPIO (External) Interrupts<br>Interrupts                                                                | 58<br>59<br>60<br>60<br>60<br>61<br>61<br>61                                                                   |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2                                                                                                                     | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration<br>infiguring GPIO (External) Interrupts                                                                              | 58<br>59<br>60<br>60<br>60<br>61<br>61<br>62<br>62                                                             |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2                                                                                                                     | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration<br>infiguring GPIO (External) Interrupts<br>Interrupts<br>Using GPIO for Wakeup from Low Power Modes<br>PIO Registers | 58<br>59<br>60<br>60<br>60<br>61<br>61<br>62<br>62<br>63                                                       |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1                                                                                                  | eneral Description<br>wer-On-Reset Configuration<br>I/O Mode and Alternate Function Selection<br>Input mode configuration<br>Output Mode Configuration<br>GPIO Drive Strength<br>ternate Function Configuration<br>infiguring GPIO (External) Interrupts<br>Interrupts<br>Using GPIO for Wakeup from Low Power Modes.                 | 58<br>59<br>60<br>60<br>60<br>61<br>61<br>62<br>62<br>63<br>63                                                 |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA                                                                                           | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>61<br>62<br>63<br>63<br><b>63</b>                                                |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 G<br>6.5.1<br>DMA<br>7.1 D                                                                                   | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>61<br>61<br>62<br>63<br>63<br>63<br>71                                           |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.3 Di                                                    | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>60<br>61<br>61<br>62<br>63<br>63<br>71<br>71<br>72<br>73                               |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 G<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.3 Di<br>7.3 Di<br>7.4 Di                                 | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>62<br>62<br>63<br>63<br>71<br>72<br>73<br>73                                     |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.3 Di<br>7.4 Di<br>7.5 Di                                         | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>61<br>62<br>62<br>63<br>71<br>72<br>73<br>73<br>73                               |

|   | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.3 Di<br>7.4 Di<br>7.5 Di<br>7.6 Cc                               | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>71<br>73<br>73<br>73<br>74<br>74                               |

| 7 | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.2 Di<br>7.3 Di<br>7.4 Di<br>7.5 Di<br>7.6 Cc<br>7.7 Cl           | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>61<br>61<br>61<br>63<br>63<br>71<br>73<br>73<br>73<br>74<br>74                   |

| 7 | 6.1 G<br>6.2 Pc<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3 Al<br>6.4 Cc<br>6.4.1<br>6.4.2<br>6.5 Gl<br>6.5.1<br>DMA<br>7.1 Di<br>7.2 Di<br>7.3 Di<br>7.3 Di<br>7.4 Di<br>7.5 Di<br>7.6 Cc<br>7.7 Cl<br>7.8 Di | eneral Description                                                                                                                                                                                                                                                                                                                    | 58<br>59<br>60<br>60<br>61<br>61<br>61<br>61<br>63<br>63<br>71<br>73<br>73<br>73<br>74<br>74<br>74<br>74<br>74 |

|    | 7.11 Cł            | nannel and Register Access Restrictions             |     |

|----|--------------------|-----------------------------------------------------|-----|

|    | 7.12               | Memory-to-Memory DMA                                |     |

|    | 7.13               | Standard DMA Control Registers                      | 77  |

|    | 7.13.1             | Standard DMA Control Register Details               | 77  |

|    | 7.15               | Standard DMA Channel O to 3 Register Base Addresses |     |

|    | 7.16               | Standard DMA Channel Configuration Register Offsets |     |

|    |                    |                                                     |     |

| ~  | 7.16.1             | 6 6                                                 |     |

| 8  | UARI               |                                                     | 84  |

|    | 8.1.1              | Features:                                           | 84  |

|    | 8.2 U,             | ART Frame Characters                                | 84  |

|    | 8.3 U,             | ART Interrupts                                      | 85  |

|    | 8.4 U              | ART Bit Rate Calculation                            | 85  |

|    | 8.4.1              | Example Baud Rate Calculation:                      | 85  |

|    | - · · · ·          | ART DMA Using the TX and RX FIFOs                   |     |

|    |                    |                                                     |     |

|    | 8.5.1              | RX FIFO DMA Operation                               |     |

|    | 8.5.2              | TX FIFO DMA Operation                               |     |

|    |                    | ushing the UART FIFOs                               |     |

|    |                    | ardware Flow Control                                |     |

|    | 8.8 U,             | ART Registers                                       |     |

|    | 8.8.1              | UART Register Details                               | 87  |

| 9  | Real-              | Time Clock (RTC)                                    | 96  |

|    | 9.1 O              | verview                                             | 96  |

|    |                    | ΓC Alarm Functions                                  |     |

|    |                    |                                                     |     |

|    | 9.2.1              | Time-of-Day Alarm                                   |     |

|    | 9.2.2              | Sub-Second Alarm                                    |     |

|    | 9.2.3              | RTC Wakeup From DEEPSLEEP/BACKUP Power Modes        |     |

|    | 9.3 R <sup>-</sup> | C Register Access                                   | 98  |

|    | 9.3.1              | RTC Register Write Protection                       |     |

|    | 9.3.2              | RTC Register Read Protection                        |     |

|    | 9.3.3              | RTC Count Register Access                           |     |

|    | 9.3.4              | RTC Alarm Register Access                           |     |

|    | 9.3.5              | RTC Trim Register Access                            |     |

|    | 9.3.6              | RTC Oscillator Control Register Access              |     |

|    | 9.4 R <sup>-</sup> | ۲C Output Pin                                       | 100 |

|    |                    | ۲C Calibration                                      |     |

|    | 9.6 R <sup>-</sup> | ۲C Registers                                        | 100 |

|    | 9.6.1              | RTC Register Details                                | 100 |

| 1( |                    | mers                                                |     |

|    |                    |                                                     |     |

|    | 10.1               | Features                                            |     |

|    | 10.2               | Basic Operation                                     |     |

|    | 10.3               | Timer Pin Functionality                             |     |

|    | 10.4               | One-Shot Mode (000b)                                |     |

|    | 10.4.1             | Timer Period                                        | 107 |

|    | 10.4.2             | 8                                                   |     |

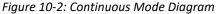

|    | 10.5               | Continuous Mode (001b)                              | 109 |

|    | 10.5.1             | Timer Period                                        | 109 |

|    | 10.5.2             |                                                     |     |

|    | 10.6               | Counter Mode (010b)                                 |     |

|    |                    |                                                     |     |

| 10.6.1   | Timer Period                                                  | 111 |

|----------|---------------------------------------------------------------|-----|

| 10.6.2   | Configuration                                                 |     |

| 10.7 I   | PWM Mode (011b)                                               |     |

| 10.7.1   | Timer Period                                                  | 113 |

| 10.7.2   | PWM Mode Configuration                                        |     |

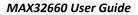

|          | Capture Mode (100b)                                           |     |

|          | •                                                             |     |

| 10.8.1   | Timer Period                                                  |     |

| 10.8.2   | Configuration                                                 |     |

| 10.9     | Compare Mode (101b)                                           |     |

| 10.9.1   | Timer Period                                                  | 117 |

| 10.9.2   | Configuration                                                 |     |

| 10.10    | Gated Mode (110b)                                             | 119 |

| 10.10.1  | Timer Period                                                  |     |

| 10.10.2  |                                                               |     |

|          | Capture/Compare Mode (111b)                                   |     |

| 10.11.1  | Timer Period                                                  |     |

| 10.11.1  |                                                               |     |

|          | Timer Registers                                               |     |

|          | -                                                             |     |

|          | Timer Register Details                                        |     |

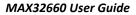

| 11 Wa    | atchdog Timer (WDT)                                           | 126 |

| 11.1 Fea | atures                                                        | 126 |

|          | age                                                           |     |

|          | errupt and Reset Period Timeout Configuration                 |     |

|          | Enabling the Watchdog Timer                                   |     |

| 11.4.1   | Enable sequence                                               | 128 |

|          | abling the Watchdog Timer                                     |     |

|          |                                                               |     |

| 11.5.1   | Manual Disable                                                |     |

| 11.5.2   | Automatic Disable                                             |     |

| 11.6 Res | setting the Watchdog Timer                                    | 128 |

| 11.6.1   | Reset Sequence                                                |     |

|          | tection of a Watchdog Reset Event                             |     |

| 11.8     | Watchdog Timer Registers                                      | 129 |

| 1.1.1    | Watchdog Timer Register Details                               |     |

|          | Master/Slave Serial Controller                                |     |

|          | -                                                             |     |

| 12.1.1   | Related Documentation                                         |     |

| 12.1.2   | I²C Bus Terminology<br>I²C Master/Slave Features              |     |

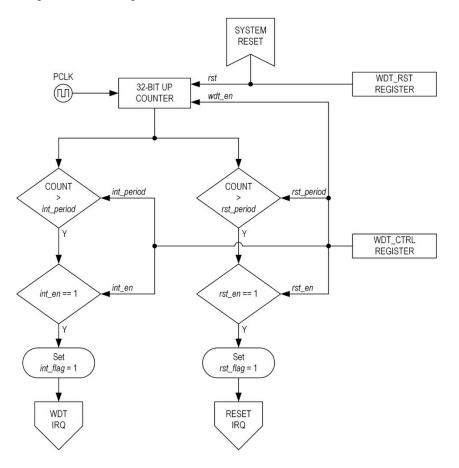

|          | I <sup>2</sup> C Overview                                     |     |

| 12.5     |                                                               |     |

| 12.3.1   | I <sup>2</sup> C Bus Speeds                                   |     |

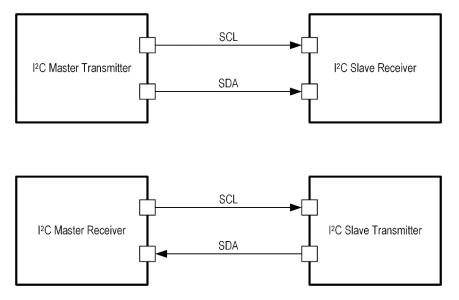

| 12.3.2   | I <sup>2</sup> C Transfer Protocol Operation                  |     |

| 12.3.3   | START and STOP Conditions                                     |     |

| 12.3.4   | Master and Slave Overview                                     |     |

| 12.3.5   | Slave Addressing                                              |     |

| 12.3.6   | Acknowledge and Not Acknowledge                               |     |

| 12.3.7   | Bit Transfer Process                                          |     |

| 12.3.8   | SCL and SDA Bus Drivers<br>I <sup>2</sup> C Interrupt Sources |     |

| 12.3.9   |                                                               |     |

| 12.3.10  |                                                               |     |

| l <sup>2</sup> C Bus Timeout                    |                                    |

|-------------------------------------------------|------------------------------------|

| I <sup>2</sup> C Addressing                     |                                    |

| I <sup>2</sup> C TX FIFO and RX FIFO Management | 139                                |

| 1 Transmit Lockout                              |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

| SCL Clock Generation for Hs-Mode                |                                    |

| TX FIFO Preloading                              |                                    |

|                                                 |                                    |

|                                                 |                                    |

| -                                               |                                    |

|                                                 |                                    |

| PI Port O                                       |                                    |

| Overview                                        | 160                                |

| I Four-Wire SPI Signals                         |                                    |

|                                                 |                                    |

|                                                 |                                    |

| ÷                                               |                                    |

| 8                                               |                                    |

|                                                 |                                    |

|                                                 |                                    |

| 6 Master Mode Serial Clock Generation           |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

| 12 SPI FIFOs                                    |                                    |

| I3 SPI Interrupts and Wakeups                   |                                    |

| SPIO Registers                                  | 169                                |

| 1 SPIO Register Details                         |                                    |

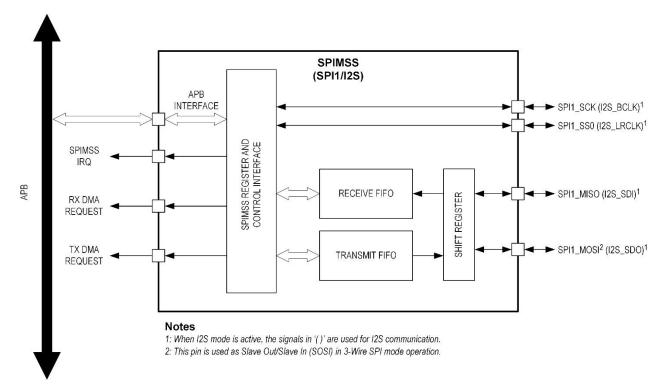

| PIMSS (SPI1/I <sup>2</sup> S)                   | 178                                |

| Overview                                        | 178                                |

| Features                                        | 178                                |

| 2 Four-Wire SPI Signals                         |                                    |

| 3 l <sup>2</sup> S Signals                      |                                    |

|                                                 |                                    |

|                                                 |                                    |

|                                                 |                                    |

| 1 Serial Clock                                  | 182                                |

|                                                 | 2       Transmit and Receive FIFOs |

| 14.3.2 SPI Slave Select Configuration                          |     |

|----------------------------------------------------------------|-----|

| 14.3.3 SPI Character Size                                      |     |

| 14.3.4 SPI Data Movement                                       |     |

| 14.3.5 SPI Master Configuration                                |     |

| 14.3.6 SPI Slave Configuration                                 |     |

| 14.4 I <sup>2</sup> S Mode                                     |     |

| 14.4.1 Mute                                                    |     |

| 14.4.2 Pause                                                   |     |

| 14.4.3 Mono                                                    | 185 |

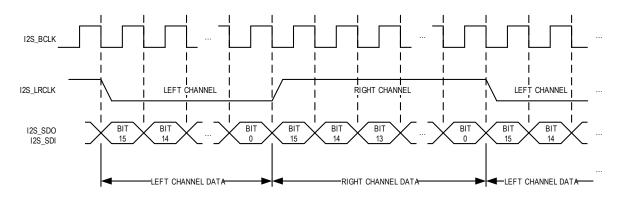

| 14.4.4 Left Justify                                            |     |

| 14.5 SPI and I <sup>2</sup> S Error Detection                  | 186 |

| 14.5.1 Transmit Overrun                                        | 186 |

| 14.5.2 SPI Slave Mode Abort                                    |     |

| 14.5.3 Receive Overrun                                         |     |

| 14.6 SPI1 and I <sup>2</sup> S Interrupts                      |     |

| 14.6.1 Data Interrupt                                          |     |

| 14.6.2 Forced Interrupt                                        |     |

| 14.6.3 Error Condition Interrupt                               |     |

| 14.6.4 Bit Rate Generator Time-out Interrupt                   |     |

| 14.7 SPIMSS Bit Rate Generator                                 |     |

| 14.7.1 SPI and I <sup>2</sup> S Slave Mode                     | 188 |

| 14.7.2 SPI and I <sup>2</sup> S Master Mode Bit Rate Generator |     |

| 14.7.3 Timer Mode                                              |     |

| 14.8 SPIMSS (SPI1/I <sup>2</sup> S) Registers                  |     |

| 14.8.1 SPIMSS Register Details                                 |     |

| 15 Trademarks                                                  |     |

| 16 Revision History                                            |     |

| ,                                                              |     |

# List of Figures

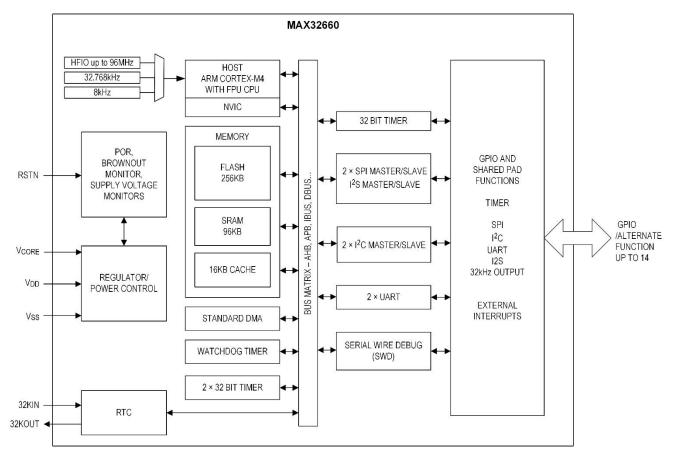

| Figure 2-1: MAX32660 High Level Block Diagram                                                               | 14  |

|-------------------------------------------------------------------------------------------------------------|-----|

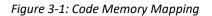

| Figure 3-1: Code Memory Mapping                                                                             |     |

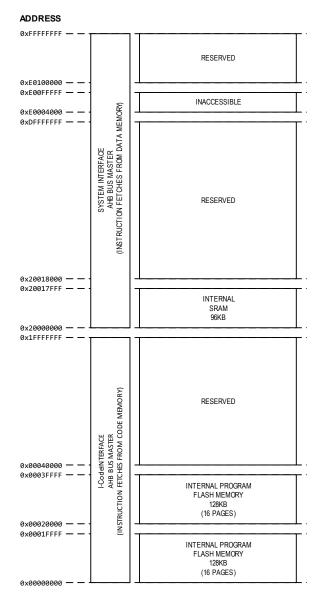

| Figure 3-2: Data Memory Map                                                                                 |     |

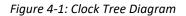

| Figure 4-1: Clock Tree Diagram                                                                              | 24  |

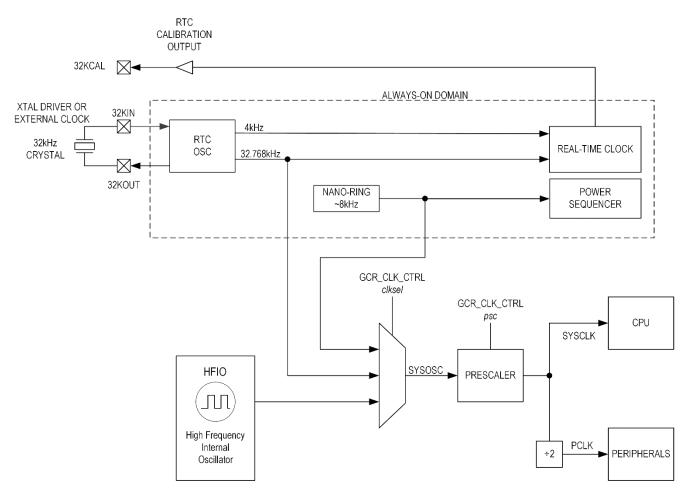

| Figure 7-1: DMAC Block Diagram                                                                              | 71  |

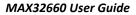

| Figure 9-1. RTC Block Diagram                                                                               | 97  |

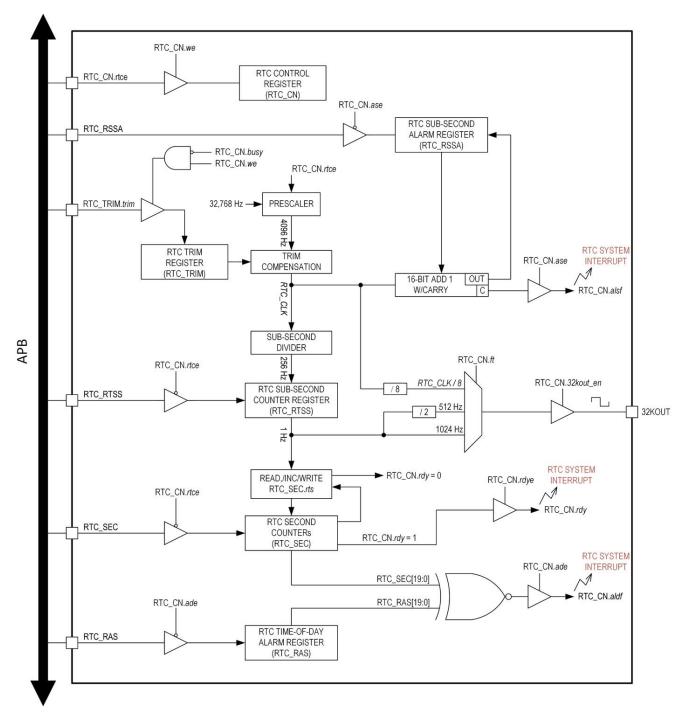

| Figure 10-1: One-Shot Mode Diagram                                                                          | 107 |

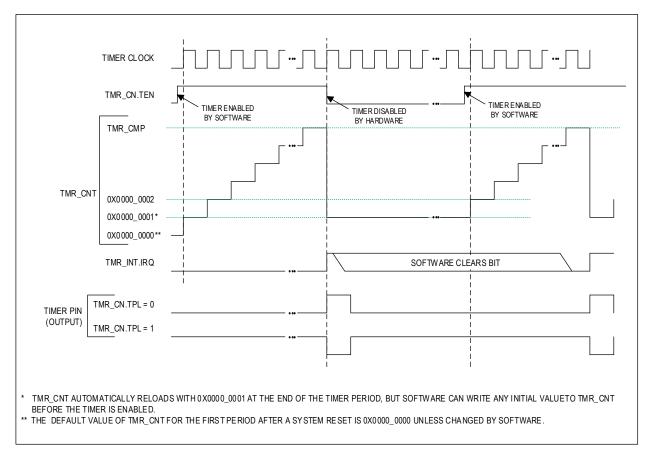

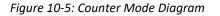

| Figure 10-2: Continuous Mode Diagram                                                                        | 109 |

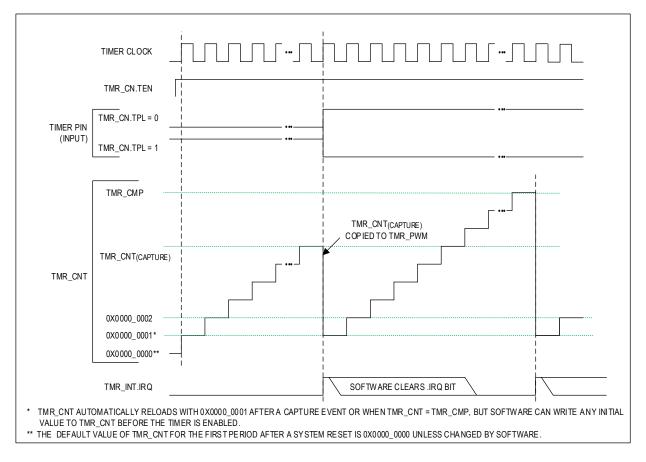

| Figure 10-3: Counter Mode Diagram                                                                           | 111 |

| Figure 10-4: Capture Mode Diagram                                                                           | 115 |

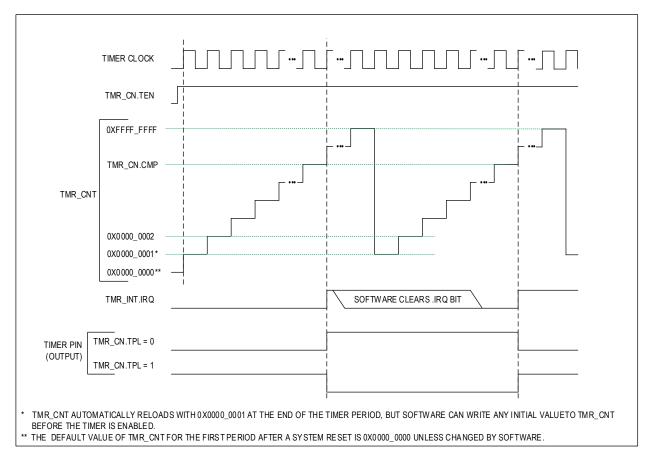

| Figure 10-5: Counter Mode Diagram                                                                           | 117 |

| Figure 10-6: Gated Mode Diagram                                                                             |     |

| Figure 11-1: Watchdog Timer Block Diagram                                                                   |     |

| Figure 12-1: The Roles of I <sup>2</sup> C Devices and the Direction the I <sup>2</sup> C Signals           | 132 |

| Figure 12-2: I <sup>2</sup> C Write Data Transfer                                                           |     |

| Figure 12-3: I <sup>2</sup> C Specification Minimum and Maximum Clock Parameters for Standard and Fast Mode |     |

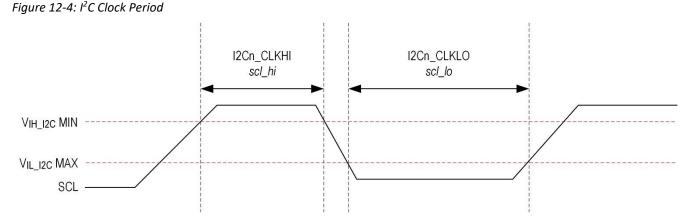

| Figure 12-4: I <sup>2</sup> C Clock Period                                                                  |     |

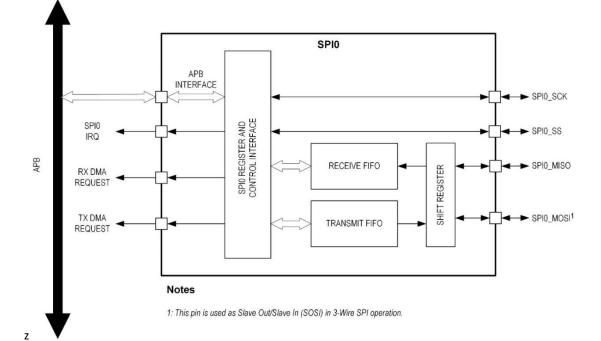

| Figure 13-1: SPIO Block Diagram                                                                             |     |

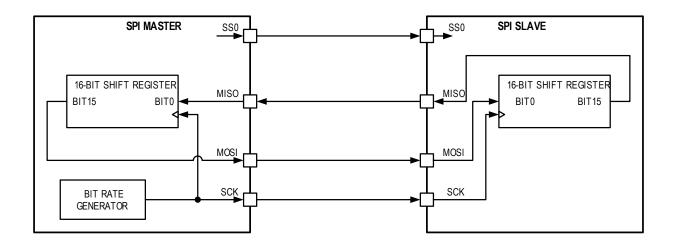

| Figure 13-2: 4-Wire SPI Connection Diagram                                                                  | 160 |

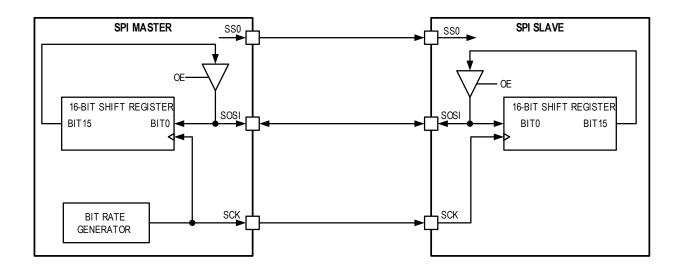

| Figure 13-3: 3-Wire SPI Connection Diagram                                                                  |     |

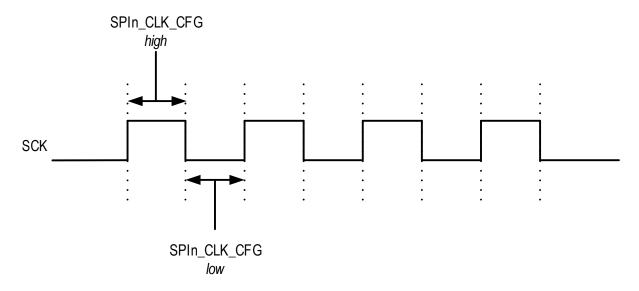

| Figure 13-4: SCK Clock Rate Control                                                                         |     |

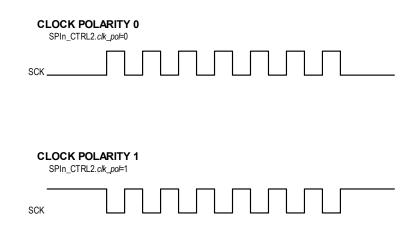

| Figure 13-5: SPI Clock Polarity                                                                             |     |

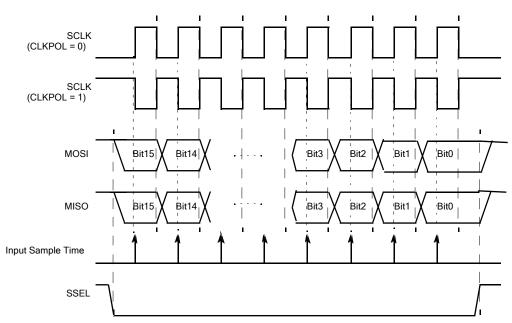

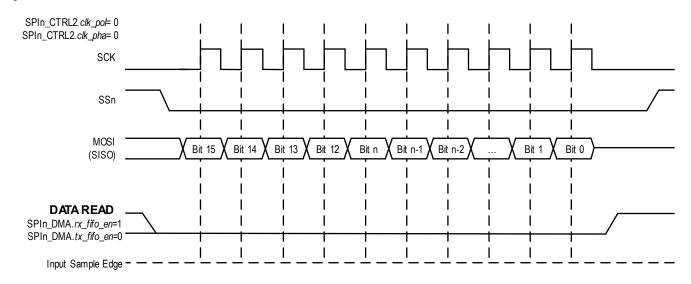

| Figure 13-6. SPI Timing (SPI0_CTRL2.clk_pha = 0)                                                            | 165 |

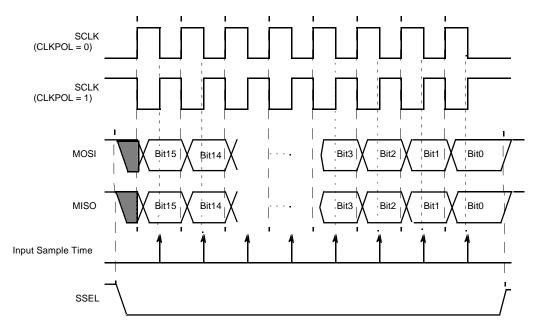

| Figure 13-7. SPI Timing (SPI0_CTRL2.clk_pha = 1)                                                            |     |

| Figure 13-8: Three-Wire SPI Read                                                                            | 167 |

| Figure 13-9: Three-Wire SPI Write                                                                           | 167 |

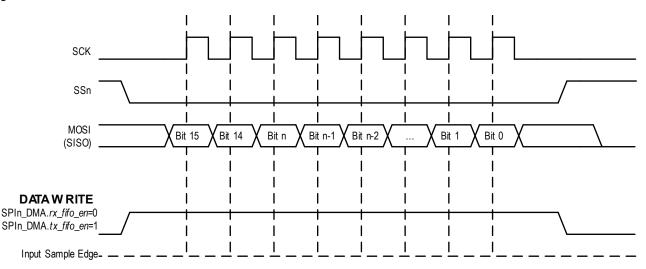

| Figure 14-1. SPIMSS Block Diagram                                                                           | 179 |

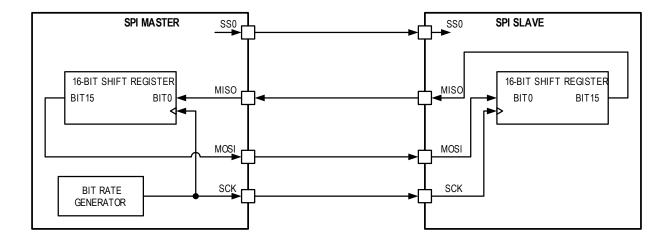

| Figure 14-2: 4-Wire SPI Connection Diagram                                                                  | 180 |

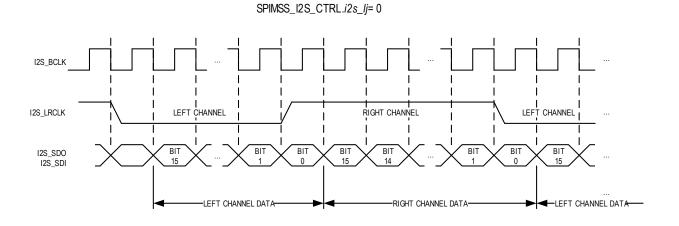

| Figure 14-3: I <sup>2</sup> S Audio Data in Standard I <sup>2</sup> S Operation                             |     |

| Figure 14-4: I <sup>2</sup> S Mode (i2s_en=1, i2s_lj=1)                                                     | 186 |

# List of Tables

| 9                                           |

|---------------------------------------------|

| 1                                           |

| 3                                           |

| 5                                           |

| 5                                           |

| 8                                           |

| 9                                           |

| 1                                           |

| 1                                           |

| 1                                           |

| 2                                           |

| 2                                           |

| 3                                           |

| 3                                           |

| 4                                           |

| 6                                           |

| 8                                           |

| 8                                           |

| 0                                           |

| 2                                           |

| 2                                           |

| 3                                           |

| 3                                           |

| 4                                           |

| 4                                           |

| 4                                           |

| 4                                           |

| 5                                           |

| 5                                           |

| 5                                           |

| 5                                           |

| 6                                           |

| 7                                           |

| 9                                           |

| 9                                           |

| 9                                           |

| 1                                           |

| 2                                           |

| 3                                           |

| 4                                           |

| 6                                           |

| 7                                           |

| 7                                           |

| 7                                           |

| 7                                           |

| 9                                           |

| 1355891112233468802233444455567999123467777 |

| Table 6-2: GPIO Port, Pin Name and Alternate Function Matrix, 20-TQFN                            | . 59 |

|--------------------------------------------------------------------------------------------------|------|

| Table 6-3: Standard GPIO Drive Strength Selection                                                | . 61 |

| Table 6-4: GPIO with I <sup>2</sup> C Alternate Function Drive Strength Selection                | . 61 |

| Table 6-5: GPIO Mode and Alternate Function Selection                                            | . 61 |

| Table 6-6: GPIO Port Interrupt Vector Mapping                                                    | . 62 |

| Table 6-7: GPIO Wakeup Interrupt Vector                                                          |      |

| Table 6-8: GPIO Port 0 Registers                                                                 |      |

| Table 6-9: GPIO Alternate Function 0 Select Register                                             |      |

| Table 6-10: GPIO Output Enable Register                                                          | . 64 |

| Table 6-11: GPIO Output Register                                                                 |      |

| Table 6-12: GPIO Input Register                                                                  |      |

| Table 6-13: GPIO Port Interrupt Mode Register                                                    | . 65 |

| Table 6-14: GPIO Port Interrupt Polarity Registers                                               | . 65 |

| Table 6-15: GPIO Port Interrupt Enable Registers                                                 | . 65 |

| Table 6-16: GPIO Interrupt Flag Register                                                         | . 66 |

| Table 6-17: GPIO Wakeup Enable Registers                                                         | . 66 |

| Table 6-18: GPIO Interrupt Dual Edge Mode Registers                                              | . 66 |

| Table 6-19: GPIO Pullup/Pulldown Enable Register                                                 | . 67 |

| Table 6-20: GPIO Alternate Function Select Register                                              | . 67 |

| Table 6-21: GPIO Input Hysteresis Enable Register                                                | . 67 |

| Table 6-22: GPIO Slew Rate Enable Register                                                       | . 67 |

| Table 6-23: GPIO Drive Strength 0 Select Register                                                | . 68 |

| Table 6-24: GPIO Drive Strength 1 Select Register                                                |      |

| Table 6-25: GPIO Pullup/Pulldown Select Register                                                 |      |

| Table 7-1: DMA Channel Registers                                                                 |      |

| Table 7-2: Channel Reload Registers                                                              |      |

| Table 7-3: Source and Destination Address Definition                                             |      |

| Table 7-4: Data movement from source to DMA FIFO                                                 | . 73 |

| Table 7-5: Data movement from the DMA FIFO to destination                                        |      |

| Table 7-6: Standard DMA Control Registers, Offsets, Access and Descriptions                      |      |

| Table 7-7: DMA Interrupt Enable Register                                                         |      |

| Table 7-8: DMA Interrupt Flag Register                                                           |      |

| Table 7-9: Standard DMA Channel 0 to Channel 15 Offsets                                          |      |

| Table 7-10: DMAn Channel Registers, Offsets, Access and Descriptions                             |      |

| Table 7-11: DMA Configuration Register                                                           |      |

| Table 7-12: DMA Status Register                                                                  |      |

| Table 7-13: DMA Source Register                                                                  |      |

| Table 7-14: DMA Destination Register                                                             |      |

| Table 7-15: DMA Count Register                                                                   |      |

| Table 7-16: DMA Source Reload Register                                                           |      |

| Table 7-17: DMA Destination Reload Register                                                      |      |

| Table 7-18: DMA Count Reload Register                                                            |      |

| Table 8-1: Example Baud Rate Calculation Results, Target Bit Rate = $1.8Mbps$ , $f_{PCLK}=48MHz$ |      |

| Table 8-2: UART Registers, Offset Addresses and Descriptions                                     |      |

| Table 8-3: UART Control 0 Register                                                               |      |

| Table 8-4: UART Control 1 Register                                                               |      |

| Table 8-5: UART Status Register                                                                  |      |

| Table 8-6: UART Interrupt Enable Register                                                        |      |

|                                                                                                  |      |

| Table 8-7: UART Interrupt Flags Register                                                     |     |

|----------------------------------------------------------------------------------------------|-----|

| Table 8-8: UART Rate Integer Register                                                        | 93  |

| Table 8-9: UART Baud Rate Decimal Register                                                   |     |

| Table 8-10: UART FIFO Register                                                               | 94  |

| Table 8-11: UART DMA Configuration Register                                                  |     |

| Table 8-12: UART TX FIFO Data Output Register                                                |     |

| Table 9-1. RTC Registers, Offsets and Descriptions                                           | 100 |

| Table 9-2: RTC Seconds Counter Register                                                      |     |

| Table 9-3: RTC Sub-Seconds Counter Register                                                  |     |

| Table 9-4: RTC Sub-Seconds Counter Register                                                  | 101 |

| Table 9-5: RTC Sub-Second Alarm Register                                                     | 101 |

| Table 9-6: RTC Control Register                                                              |     |

| Table 9-7: RTC Trim Register                                                                 |     |

| Table 10-1: Timer Register Offsets, Names, Access and Descriptions                           | 122 |

| Table 10-2: Timer Count Registers                                                            |     |

| Table 10-3: Timer Compare Registers                                                          | 122 |

| Table 10-4: Timer PWM Registers                                                              |     |

| Table 10-5: Timer Interrupt Registers                                                        | 123 |

| Table 10-6: Timer Control Registers                                                          |     |

| Table 11-1: Watchdog Timer Interrupt Period with $f_{SYSCLK}$ = 96MHz and $f_{PCLK}$ = 48MHz |     |

| Table 11-2: Watchdog Timer Registers                                                         |     |

| Table 11-3: Watchdog Timer Control Register                                                  | 129 |

| Table 11-4: Watchdog Timer Reset Register                                                    | 130 |

| Table 12-1: I <sup>2</sup> C Bus Terminology                                                 | 131 |

| Table 12-2: I <sup>2</sup> C Address Byte Format                                             |     |

| Table 12-3: I <sup>2</sup> C Registers                                                       |     |

| Table 12-4: I <sup>2</sup> C Control Registers 0                                             |     |

| Table 12-5: I <sup>2</sup> C Status Registers                                                |     |

| Table 12-6: I <sup>2</sup> C Interrupt Status Flags Registers 0                              |     |

| Table 12-7: I <sup>2</sup> C Interrupt Enable 0 Registers                                    |     |

| Table 12-8: I <sup>2</sup> C Interrupt Status Flags 1 Registers                              |     |

| Table 12-9: I <sup>2</sup> C Interrupt Enable Registers 1                                    |     |

| Table 12-10: I <sup>2</sup> C FIFO Length Registers                                          |     |

| Table 12-11: I <sup>2</sup> C Receive Control Registers 0                                    |     |

| Table 12-12: I <sup>2</sup> C Receive Control 1 Registers                                    |     |

| Table 12-13: I <sup>2</sup> C Transmit Control Registers 0                                   |     |

| Table 12-14: I <sup>2</sup> C Transmit Control Registers 1                                   |     |

| Table 12-15: I <sup>2</sup> C Data Registers                                                 |     |

| Table 12-16: I <sup>2</sup> C Master Mode Control Registers                                  |     |

| Table 12-17: I <sup>2</sup> C SCL Low Control Register                                       |     |

| Table 12-18: I <sup>2</sup> C SCL High Control Register                                      |     |

| Table 12-19: I <sup>2</sup> C Timeout Registers                                              |     |

| Table 12-20: I <sup>2</sup> C Timeout Registers                                              |     |

| Table 12-21: I <sup>2</sup> C Slave Address Register                                         |     |

| Table 12-22: I <sup>2</sup> C DMA Register                                                   |     |

| Table 13-1: Four-Wire SPI Signals                                                            |     |

| Table 13-2: Three-Wire SPI Signals                                                           |     |

| Table 13-3: SPIO Pins                                                                        | 162 |

|                                                                                              |     |

| Table 13-4. Clock Phase and Polarity Operation               |     |

|--------------------------------------------------------------|-----|

| Table 13-5: SPIO Master Register Addresses and Descriptions  | 169 |

| Table 13-6: SPI FIFO Data Registers                          | 169 |

| Table 13-7: SPI Master Signals Control Registers             | 169 |

| Table 13-8: SPI Transmit Packet Size Register                | 171 |

| Table 13-9: SPI Static Configuration Registers               | 171 |

| Table 13-10: SPI Slave Select Timing Register                | 172 |

| Table 13-11: SPI Master Clock Configuration Registers        | 172 |

| Table 13-12: SPI DMA Control Registers                       | 173 |

| Table 13-13: SPI Interrupt Flag Registers                    | 174 |

| Table 13-14: SPI Interrupt Enable Registers                  |     |

| Table 13-15: SPI Wakeup Status Flags Registers               | 177 |

| Table 13-16: SPI Wakeup Enable Registers                     | 177 |

| Table 13-17: SPI Status Registers                            | 177 |

| Table 14-1: Four-Wire SPI Signals                            | 179 |

| Table 14-2: I <sup>2</sup> S Signals                         | 180 |

| Table 14-3: SPIMSS Pins for SPI1 and I <sup>2</sup> S        | 181 |

| Table 14-4. Clock Phase and Polarity Operation               | 182 |

| Table 14-5: SPIMSS Register Offsets, Access and Descriptions | 189 |

| Table 14-6. SPIMSS Data Register                             |     |

| Table 14-7: SPIMSS Control Register                          | 189 |

| Table 14-8: SPIMSS Interrupt Flag Register                   |     |

| Table 14-9: SPIMSS Mode Register                             | 191 |

| Table 14-10: SPIMSS Bit Rate Generator Register              | 192 |

| Table 14-11: SPIMSS DMA Register                             | 192 |

| Table 14-12: SPIMSS I <sup>2</sup> S Control Register        | 101 |

# 1 Introduction

For ordering information, mechanical and electrical characteristics for the MAX32660 family of devices please refer to the datasheet. For information on the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core, please refer to the *Cortex*-M4 with FPU *Technical Reference Manual*.

# **1.1** Related Documentation

The MAX32660 datasheet and errata are available from the Maxim Integrated website, <u>http://www.maximintegrated.com</u>.

# 2 Overview

The MAX32660 is an ultra-low power, cost effective highly integrated microcontroller designed for battery-powered devices and wireless sensors. It combines a flexible and versatile power management unit with the powerful Arm Cortex-M4 with FPU (Floating Point Unit). The device enables designs with complex sensor processing without compromising battery life. It also offers legacy designs an easy and cost optimal upgrade path from 8 or 16-bit microcontrollers. The device integrates up to 256KB of flash memory and 96KB of SRAM to accommodate application and sensor code.

The device features four powerful and flexible power modes. It can operate from a single supply battery voltage, or a dual supply typically provided by a PMIC. The I<sup>2</sup>C (Inter-Integrated Circuit) port supports standard, fast, fast-plus and high-speed modes operating up to 3400Kbps. The SPI ports can run up to 48MHz in both master and slave mode, and the UARTs can run up to 4Mbps. Three general-purpose 32-bit timers, a watchdog timer, and a real-time clock are also provided. An I<sup>2</sup>S (Inter-IC Sound) interface provides audio streaming to or from an external audio codec.

#### Figure 2-1: MAX32660 High Level Block Diagram

# 3 Memory, Register Mapping, and Access

# 3.1 Overview

The Arm Cortex-M4 with FPU core defines a standard memory space for unified code and data access. This memory space is addressed in units of single bytes but is most typically accessed in 32-bit (4 byte) units. It may also be accessed, depending on the implementation, in 8-bit (1 byte) or 16-bit (2 byte) widths. The total range of the memory space is 32-bits in width (4GB addressable total), from addresses 0x0000 0000 to 0xFFFF FFFF.

It is important to note, however, that the architectural definition does not require the entire 4GB memory range to be populated with addressable memory instances.

#### Figure 3-2: Data Memory Map

| 0046000 | SPI0                       |

|---------|----------------------------|

| 0044000 | RESERVED                   |

| 0042000 | UART (0,1)                 |

| 0028000 | RESERVED                   |

| 002A000 | INTERNAL CACHE CONTROLLER  |

| 0029400 | RESERVED                   |

| 0029000 | FLASH CONTROLLER           |

| 0028000 | STANDARD DMA               |

| 001F000 | RESERVED                   |

| 001D000 | I2C (0,1)                  |

| 001A000 | RESERVED                   |

| 0019000 | SPIMSS(I2S)                |

| 0013000 | RESERVED                   |

| 0010000 | TIMER (0,1,2)              |

| 0009000 | RESERVED                   |

| 0008000 | GPIO PORT 0                |

| 0006C00 | RESERVED                   |

| 0006800 | POWER SEQUENCER            |

| 0006400 | RESERVED                   |

| 0006000 | RTC                        |

| 0003400 | RESERVED                   |

| 0003000 | WATCHDOG TIMER 0           |

| 0000C00 | RESERVED                   |

| 0000800 | FUNCTION CONTROL REGISTERS |

| 0000400 | SI REGISTERS               |

| 0000000 | GLOBAL CONTROL REGISTERS   |

# **3.2 Standard Memory Regions**

Many standard memory regions are defined for the Arm Cortex-M4 architecture; the use of many of these is optional for the system integrator. At a minimum, the MAX32660 must contain code and data memory for application code, stack and heap usage, as well as certain components which are part of the implemented architecture.

### 3.2.1 Code Space

The code space area of memory is designed to contain the primary memory used for code execution by the device. This memory area is defined from byte address range 0x0000 0000 to 0x1FFF FFFF (0.5GB maximum). Two different standard core bus masters are used by the Arm Cortex-M4 core and the Arm debugger to access this memory area. The I-Code AHB bus master is used for instruction decode fetching from code memory, while the D-Code AHB bus master is used for data fetches from code memory. This is arranged so that data fetches avoid interfering with instruction execution.

On the MAX32660, the code space memory area contains the main internal flash memory that typically contains the instruction code that will be executed on the device. The internal flash memory is mapped into both code and data space from 0x0000 0000 to 0x0003 FFFF. This program memory area must also contain the default system vector table and the initial settings for all system exception handlers and interrupt handlers. The reset vector for the device is 0x0000 0000.

### 3.2.2 SRAM Space

The SRAM area of memory is intended to contain the primary SRAM data memory of the device and is defined from byte address range 0x2000 0000 to 0x3FFF FFFF (0.5GB maximum). This memory can be used for general purpose variable and data storage, code execution, and the Arm Cortex-M4 stack.

On the MAX32660, this memory area contains the main system SRAM 96KB, which is mapped from 0x2000 0000 to 0x2001 7FFF.

The entirety of the SRAM memory space on the MAX32660 is contained within the dedicated Arm Cortex-M4 with FPU's SRAM bit-banding region from 0x2000 0000 to 0x200F FFFF (1MB maximum for bit-banding). This means that the CPU can access the entire SRAM either using standard byte/word/doubleword access or using bit-banding operations. The bit-banding mechanism allows any single bit of any given SRAM byte address location to be set, cleared, or read individually by reading from or writing to a corresponding doubleword (32-bit wide) location in the bit-banding alias area.

The alias area for the SRAM bit-banding is located beginning at 0x2200 0000 and is a total of 32MB maximum, which allows the entire 1MB bit banding area to be accessed. Each 32-bit (4 byte aligned) address location in the bit-banding alias area translates into a single bit access (read or write) in the bit-banding primary area. Reading from the location performs a single bit read, while writing either a 1 or 0 to the location performs a single bit set or clear.

Note: The Arm Cortex-M4 with FPU translates the access in the bit-banding alias area into the appropriate read cycle (for a single bit read) or a read-modify-write cycle (for a single bit set or clear) of the bit-banding primary area. This means that bit-banding is a core function (i.e., not a function of the SRAM memory interface layer or the AHB bus layer), and thus is only applicable to accesses generated by the core itself. Reads/writes to the bit-banding alias area by other (non-Arm -core) bus masters such as the Standard DMA AHB bus master will not trigger a bit-banding operation and will instead result in an AHB bus error.

The SRAM area on the MAX32660 is capable code execution. Code stored in the SRAM is accessed directly for execution using the system bus and is not cached. The SRAM is where the Arm Cortex-M4 stack must be located, as it is the only general-purpose SRAM memory on the device. A valid stack location inside the SRAM must be set in the vector table stored at address 0x0000 0000 in the internal flash memory. Refer to the *Cortex-M4 with FPU Technical Reference Manual*. The MAX32660 specific AHB Bus Masters can also access the SRAM to use as general storage or working space.

### 3.2.3 Peripheral Space

The peripheral space area of memory is intended for mapping of control registers, internal buffers/working space, and other features needed for the firmware control of non-core peripherals. It is defined from byte address range 0x4000 0000 to 0x5FFF FFFF (0.5GB maximum). On the MAX32660, all device-specific module registers are mapped to this memory area, as well as any local memory buffers or FIFOs which are required by modules.

As with the SRAM region, there is a dedicated 1MB area at the bottom of this memory region (from 0x4000 0000 to 0x400F FFFF) that is used for bit-banding operations by the Arm Cortex-M4 with FPU. Four-byte-aligned read/write operations in the peripheral bit-banding alias area (32MB in length, from 0x4200 0000 to 0x43FF FFFF) are translated by the core into read/mask/shift or read/modify/write operation sequences to the appropriate byte location in the bit-banding area.

Note: The bit-banding operation within peripheral memory space is, like bit-banding function in SRAM space, a core remapping function. As such, it is only applicable to operations performed directly by the Arm Cortex-M4 core. If another memory bus master (such as the Standard DMA AHB master) accesses the peripheral bit-banding alias region, the bit-banding remapping operation will not take place. In this case, the bit-banding alias region will appear to be a non-implemented memory area (causing an AHB bus error).