LT1952

### DESCRIPTION

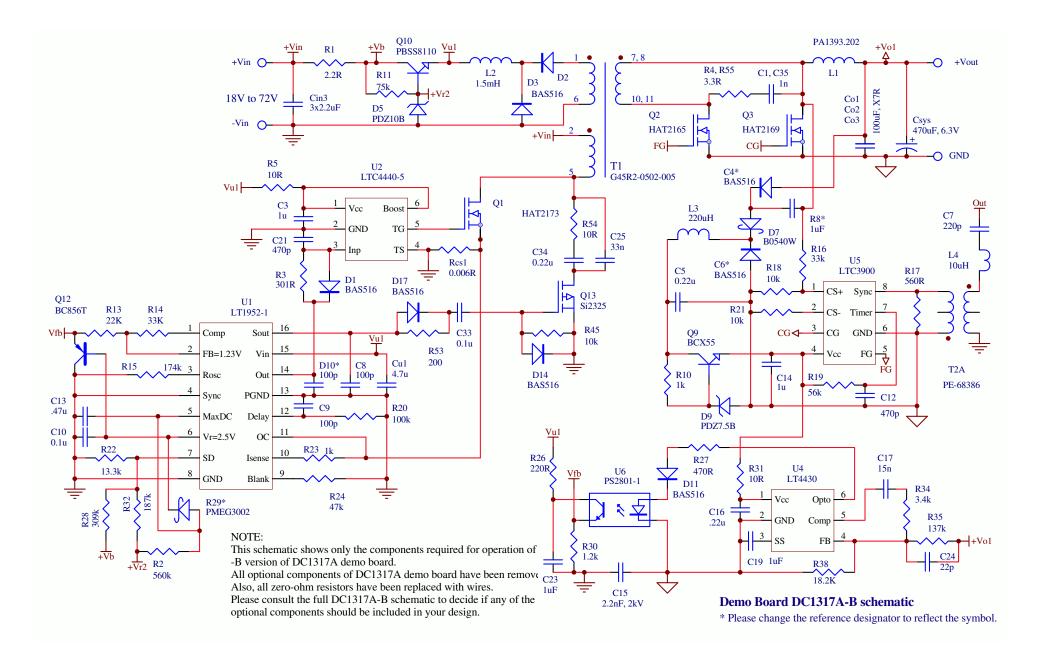

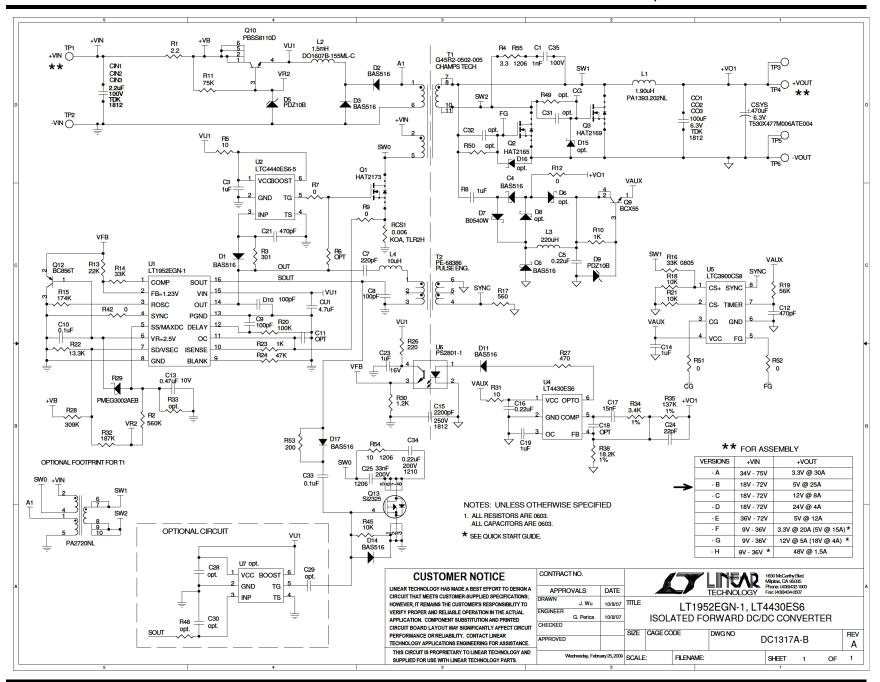

Demonstration circuit 1317A-B is isolated input to high current output 1/8th Brick footprint converter featuring the LT®1952 switching controller with Active Reset circuit. The Active Reset circuit can improve the efficiency in wide input voltage applications. Also, the Active Reset allows the implementation of self-driven synchronous secondary rectifiers in some applications.

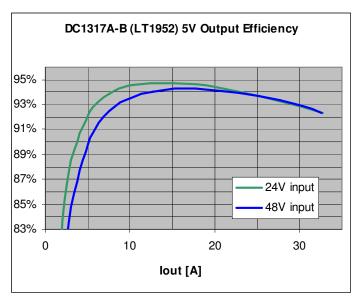

The DC1317A-B converts isolated wide 18V to 72V input to 5V output and provides over 30A of output current depending on cooling. When determining the cooling requirements the actual input voltage range and continuous maximum output current must be taken into account. The converter operates at 200kHz with the peak efficiency greater than 94%. The DC1317 can be easily modified to generate output voltages in the range from 0.6V to 48V. The output currents are limited by total output power of up to 150W.

The available versions of DC1317A are: DC1317A-A, 34-75Vin to 3.3V, 35A DC1317A-B, 18-72Vin to 5V, 25A DC1317A-C, 18-72Vin to 12V, 10A

DC1317A-D, 18-72Vin to 24V, 5A DC1317A-E, 36-72Vin to 5V, 12A DC1317A-F, 9-36Vin to 3.3V, 20A DC1317A-G, 9-36Vin to 12V, 5A DC1317A-H, 9-36Vin to 48V, 1.5A

The DC1317 circuit features soft-start which prevents output voltage overshoot on startup or when recovering from overload condition.

The DC1317 has precise over-current protection circuit that allows for continuous operation under short circuit conditions. The low power dissipation under short circuit conditions insures high reliability even during short circuits.

The LT1952 can be synchronized to an external clock of up to 400kHz. Please refer to LT1952 data sheet for design details and applications information.

Design files for this circuit board are available. Call the LTC factory.

LT is a trademark of Linear Technology Corporation

Table 1. Performance Summary

| PARAMETER                              | CONDITION                                                           | VALUE                |

|----------------------------------------|---------------------------------------------------------------------|----------------------|

| Minimum Input Voltage                  | I <sub>OUT</sub> = 0A to 25A                                        | 18V                  |

| Maximum Input Voltage                  | I <sub>OUT</sub> = 0A to 25A                                        | 72V                  |

| Vout                                   | V <sub>IN</sub> = 18V to 72V, I <sub>OUT</sub> = 0A to 25A (30Amax) | 5V ±3%               |

| Typical Output Ripple V <sub>OUT</sub> | V <sub>IN</sub> = 18V to 72V, I <sub>OUT</sub> = 0A to 25A          | 50mV <sub>P</sub> _P |

| Nominal Switching Frequency            |                                                                     | 200kHz               |

### QUICK START PROCEDURE

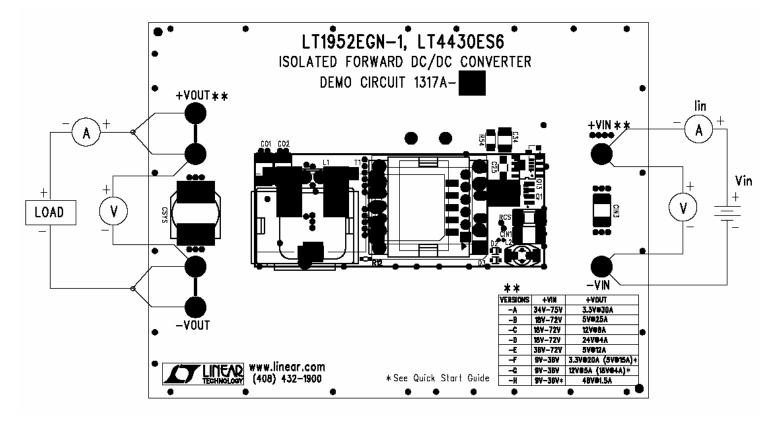

Demonstration circuit 1317 is easy to set up to evaluate the performance of LT1952 circuit. **Refer to Figure 1 for proper measurement equipment setup** and follow the procedure below:

**NOTE:** When measuring the input or output voltage ripple, care must be taken to avoid a long ground lead on the oscilloscope probe. Measure the input or output voltage ripple by touching the probe tip directly across the Vin or Vout and GND terminals. See Figure 2. for proper scope probe technique.

- 1. With power off, connect the input power supply to Vin and GND. Make sure that the input power supply has sufficient current rating at minimum input voltage for the required output load.

- 2. Turn on the power at the input.

**NOTE:** Make sure that the input voltage does not exceed 72V.

- **3.** Check for the proper output voltage. Vout = 5V.

- If there is no output, temporarily disconnect the load to make sure that the load is not set too high.

- 4. Once the proper output voltage is established, adjust the load within the operating range and observe the output voltage regulation, ripple voltage, efficiency and other parameters.

- 5. The DC1317 is equipped with an output capacitor CSYS (470uF) that approximates typical system rail capacitance. If system board already has capacitance of similar value CSYS can be removed.

2

Figure 1. Proper Measurement Equipment Setup

Figure 2. Scope Probe Placement for Measuring Input or Output Ripple

#### **ACTIVE RESET CIRCUIT**

The Active Reset circuit on DC1317A-B demo board consists of a small P-Channel MOSFET Q13 and reset capacitor C25. The MOSFET Q13 is used to connect the reset capacitor across the transformer T1 primary winding during the reset period when Q1 MOSFET is off. The voltage across capacitor C25 automatically adjusts with the duty cycle to provide complete transformer reset under all operating conditions.

Also the active reset circuit shapes the reset voltage into a square waveform that results in lower drain voltages for Q1 and Q2 MOSFETs. The lower MOSFET drain voltages allow lower voltage and lower Rdson MOSFETs to be used. The MOSFETs must be avalanche rated for the peak reset voltage. If non-avalanche rated MOSFETs are used a proper drain voltage derating should be used.

The main benefit of active reset circuit in the case of DC1317A-B demo board is high efficiency (shown in Figure 3), wide input range, high power density

and small size. To achieve such high efficiency all of the power components were carefully selected. Please consult LT factory for assistance if any changes to the circuit are required.

Figure 3. High efficiency of DC1317A-B allows the board to be used in thermally critical applications

#### **OUTPUT LOAD STEP RESPONSE**

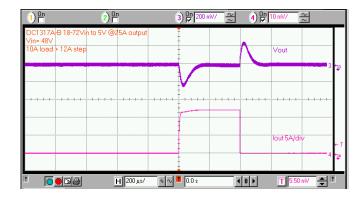

The load step response of DC1317A-B, shown in Figure 4, is very fast even though relatively small amount of output capacitance is present (300uF ceramic and 470uF electrolytic). This is thanks to fast error amplifier of LT4430, optimal amount of current slope compensation of LT1952, fast opto coupler and fast error amplifier of LT1952. If higher load steps need to be handled more output capacitance can be added in order to keep the voltage transients at the desired level. Also, the loop response can be improved further by faster loop compensation.

Figure 4. Fast transient response of DC1317 is superior to many competing power modules without the additional output capacitors.

#### **SOFT START FUNCTION**

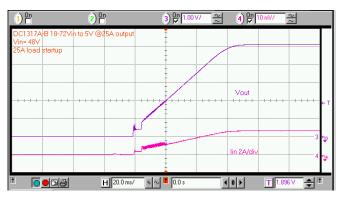

The DC1317 features LT4430 opto coupler driver that has soft start function which produces monotonic startup ramp shown if Figure 5. The rise time of output voltage is controlled by capacitor C19 that is connected to OC (Overshoot Control) pin of LT4430. Also, the soft-start function will prevent input current surges even with full load at the output.

Figure 5. The LT4430 opto coupler driver produces monotonic output voltage rise at startup without output voltage overshoot.

#### **DEBUGGING AND TESTING**

The DC1317 can easily be tested and debugged by powering the bias circuit separately from the main power circuit. To place DC1317 into debug mode

remove the resistor R1 and connect 48V, 100mA power source to +Vb node (right side of R1). By doing this, the primary PWM controller LT1952 can be activated without the main primary power being applied to +Vin.

To activate the secondary side control circuit LT4430 diode OR a 10V, 100mA power source into collector of Q9 bias transistor.

Once the primary and secondary controllers are running the main power (+Vin) can be applied slowly while observing the switching waveforms and output voltage.

The input current supplying the power transformer T1 should not exceeded 100mA without the output load. If one of the MOSFETs is damaged, the input current will exceed 100mA.

#### **PCB LAYOUT**

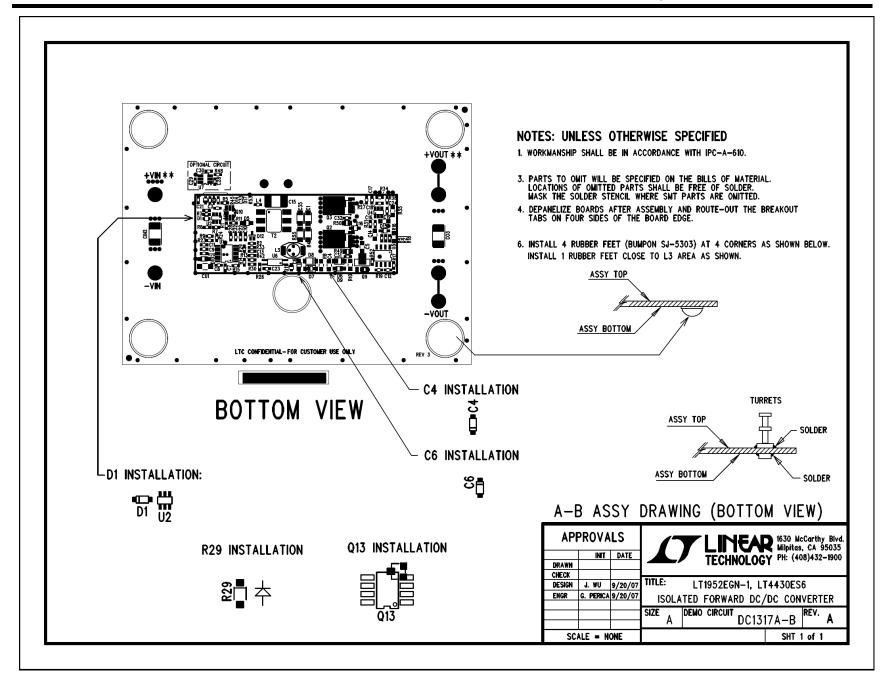

The pcb layout should be carefully planned to avoid potential noise problems. The PCB layout for DC1317A can be used as a guide. Since demo board DC1317A has 8 versions the PCB layout has optional components that can be removed. Also, the PCB layout has a common schematic that is used just for the layout. The actual circuit schematic shows component values. The PCB layout schematic does not show the component values.

In some cases, a different component like a diode is used in a place holder for a capacitor such as in the case of C6. Please modify the reference designators in your schematic to reflect the actual component used. The following simple PCB layout rules should be helpful.

If possible use solid ground planes on layers 2 and n-1. The ground planes will prevent the switching noise from coupling into sensitive lines.

Place sensitive lines on the inner layers that will be shielded by grounds on layers 2 and n-1.

Keep the loop formed by Q1, RCS1, Cin and T1 tight.

Keep the loop formed by Q2, Q3 and T1 tight.

Keep noise sensitive nodes like SD/VSEC, ROSC, FB, COMP, ISENSE, BLANK and DELAY as small as posible by placing the associated components close to the LT1952 and LT4430 chips.

Use local vias for all components that connect to ground planes.

Do not place any traces on the layers 2 and n-1 to avoid ground planes from being compromised.

If the PCB layout has to be done on 2 or 4-layer PCB try to stay close to the guidelines outlined above. Also, maximize the ground connections between components by placing the components tight together.

Please contact LT factory for additional assistance.

5