# Using the ACS760 Evaluation Board

#### Introduction

The ACS760 is a 240 V\*A protection IC with integrated hot-swap gate driver and internal 1.5 m $\Omega$  Hall effect based current monitor. Complete device description is available on the Allegro® website, www.allegromicro.com. This application note describes the evaluation board supplied by Allegro for demonstrating the capabilities of the ACS760 in various customer applications.

## **Description**

The ACS760 evaluation board only requires a single user-provided 12 V source to power the board and device. For ease of use, on-board banana plugs may be used to connect the 12 V source to the board, and to apply a load.

The on-board A8498 regulator and associated circuitry, located on the back of the evaluation board, is used to provide the second 3.3 V rail. This 3.3 V rail is used for the fault pull-ups as well as to enable the device. To enable the ACS760, a jumper must be placed between +3.3 V and EN on the Molex connector.

To provide a more friendly customer interface, LEDs located on the top of the board will light for fault condition output signals on the OPDLY, OCDLY, FAULT, and S1SHORT pins. Test points are also provided for the following pins: EN, VIOUT, ISET, CG, OCDLY, OPDLY, FAULT, S1FAULT, GND, and GATE. These inputs and outputs are described in the Terminal List table on the next page.

This evaluation board also gives the customer the ability to configure the ACS760 to operate in pure current mode. To do so, place a shunt across jumper J2. This shorts the

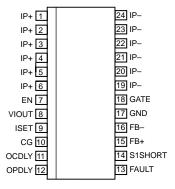

Figure 1. The Allegro ACS760 is provided in a compact, 24-pin QSOP package

OPDLY pin to GND, allowing the I<sub>PF</sub> upper trip level to be set by adjusting the resistor connected between the ISET pin and GND.

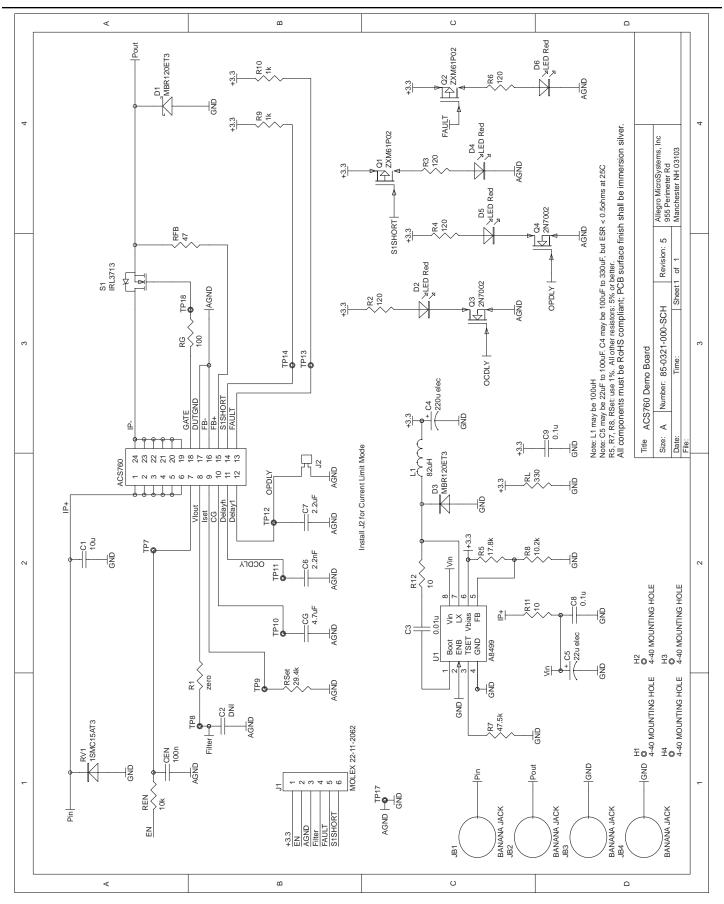

The typical component values are shown in the ACS760 evaluation board schematic (figure 3). A pin-out diagram and Terminal List table is provided. In addition to the information found in the datasheet, a fault description table is included below.

For additional information, please contact your local Allegro field application office.

(A)

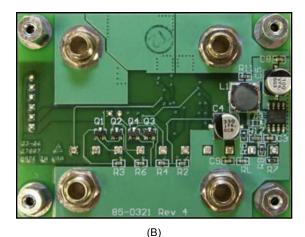

Figure 2. The Allegro ACS760 Evaluation board. A: top side, with test points and LEDs. B: bottom side.

Figure 3. The Allegro ACS760 Evaluation board schematic diagram

### **Pin-out Diagram**

#### **Terminal List Table**

| Number | Name    | Function                                                                                                                                                                                                                                                                                                                          |  |  |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1-6    | IP+     | Primary sensed current conduction path input; power input pins: connected to V <sub>CC</sub>                                                                                                                                                                                                                                      |  |  |

| 7      | EN      | Enable pin. Toggling this pin to the low state after a FAULT condition resets the ACS760.                                                                                                                                                                                                                                         |  |  |

| 8      | VIOUT   | Analog current sense output. Output voltage on this pin is proportional to the current flowing from the IP+ pins to the IP- pins.                                                                                                                                                                                                 |  |  |

| 9      | ISET    | Terminal for R <sub>SET</sub> resistor. Sets Fault Current Threshold, I <sub>PF</sub> , via external resistor, R <sub>SET</sub> , connected between this terminal and GND. Factory trimmed 100 µA current source flows out of this pin.                                                                                           |  |  |

| 10     | CG      | Terminal for $C_G$ capacitor. May be used to adjust the turn-on time and soft start control of an external MOSFET, S1. Voltage on this pin limits inrush current through MOSFET S1. Set via external capacitance, $C_G$ , connected between this pin and GND. This capacitor is charged by an internal 20 $\mu$ A current source. |  |  |

| 11     | OCDLY   | Terminal for external capacitor, $C_{OCD}$ , Used to adjust delay for overcurrent shutdown, set via the external capacitor, $C_{OCD}$ , connected between this pin and GND.                                                                                                                                                       |  |  |

| 12     | OPDLY   | Terminal for external capacitor, $C_{OPD}$ , Used to adjust delay for overpower shutdown, set via the external capacitor, $C_{OPD}$ , connected between this pin and GND.                                                                                                                                                         |  |  |

| 13     | FAULT   | Active low; output signal for short circuit and 240 V*A overload faults; does not trip for S1 short circuit fault. Connect a 1 k $\Omega$ pull-up resistor between this pin and the 3.3 V rail.                                                                                                                                   |  |  |

| 14     | S1SHORT | Active low; output signal for MOSFET S1 failure. Connect a 1 k $\Omega$ pull-up resistor between this pin and the 3.3 V rail.                                                                                                                                                                                                     |  |  |

| 15     | FB+     | Input of positive feedback on output voltage. Used to determine 240 V*A threshold by difference between FB+ and FB– pins.                                                                                                                                                                                                         |  |  |

| 16     | FB-     | Input of negative feedback on output voltage. Used to determine 240 V*A threshold by difference between FB+ and FB- pins. Pulling the FB- pin to 3.3 V, and the OPDLY pin to GND, disables the 240 V*A power fault, which allows the ACS760 to operate purely in Current Mode.                                                    |  |  |

| 17     | GND     | Terminal for ground connection.                                                                                                                                                                                                                                                                                                   |  |  |

| 18     | GATE    | Terminal for external MOSFET, S1. Provides output voltage to drive S1. Current through S1 is controlled at start-up by external capacitance connected between the CG pin and GND.                                                                                                                                                 |  |  |

| 19-24  | IP-     | Primary sensed current conduction path output; power output pins.                                                                                                                                                                                                                                                                 |  |  |

**Fault Description Table**

|                                                | lpF Fault                                       | Overcurrent Fault            |                                |

|------------------------------------------------|-------------------------------------------------|------------------------------|--------------------------------|

| 240 V*A Power Fault                            | (Soft Short)                                    | (Hard Short)                 | S1 Short                       |

| -FAULT pin falls low when                      | -User may set IpF fault current                 | –50 mΩ load to GND           | -If the gate on the external   |

| power supply load > 240 V*A                    | threshold (nominally 30 to                      | -The ACS760 pulls down       | MOSFET is low and more         |

| <ul><li>–Adding an external cap from</li></ul> | 40 A) via resistor from ISET                    | the external MOSFET gate     | than 2.1 A flows through the   |

| OCPDLY to GND adjusts delay                    | pin to GND                                      | approximately 2 µs after the | ACS760, the S1SHORT signal     |

| for over-power shutdown                        | –FAULT pin falls low when                       | load current exceeds the     | pin falls to the low state     |

|                                                | current exceeds IpF fault                       | overcurrent fault threshold  | –Unlike the 240 V*A            |

|                                                | current threshold                               |                              | Power fault, lpF fault, and    |

|                                                | <ul> <li>Adding an external cap from</li> </ul> |                              | Overcurrent fault, the EN pin  |

|                                                | the OCDLY pin to GND adjusts                    |                              | may not be cycled to reset the |

|                                                | the delay for overcurrent                       |                              | S1 Short signal; power to the  |

|                                                | shutdown                                        |                              | device must be cycled          |

$Copyright \ @2006, 2007, Allegro \ Micro Systems, Inc.$

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com